## DRAWINGS

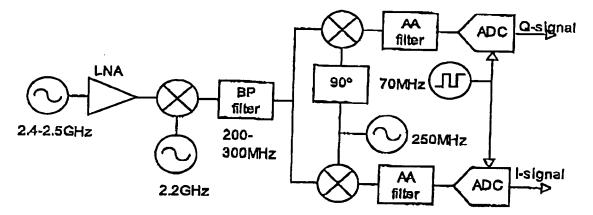

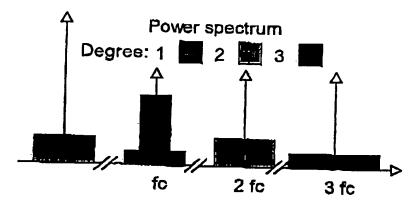

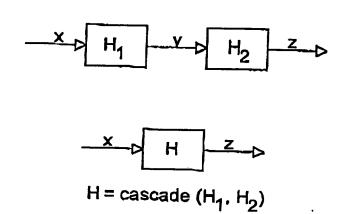

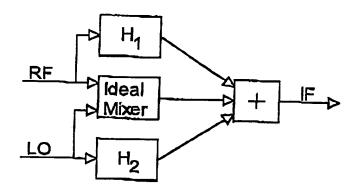

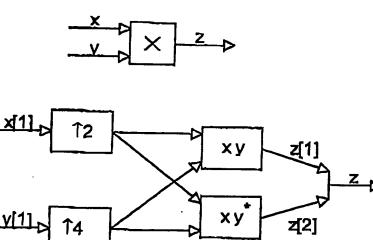

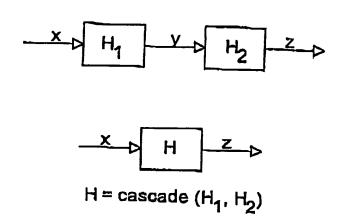

Figure 1

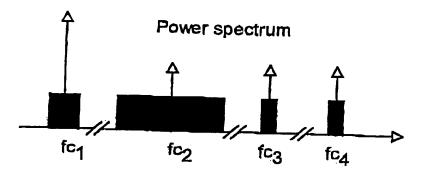

Figure 2

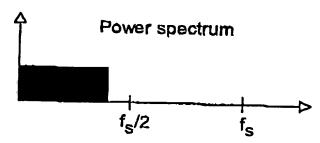

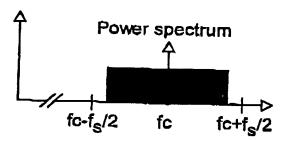

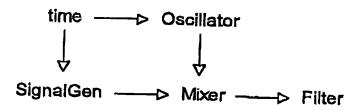

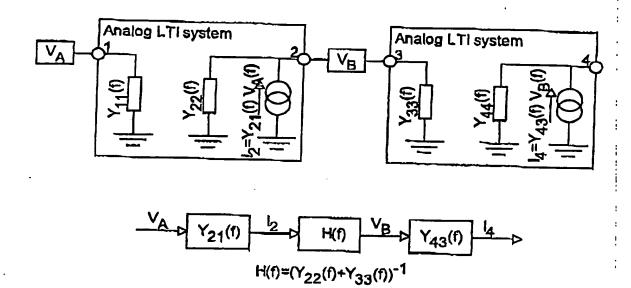

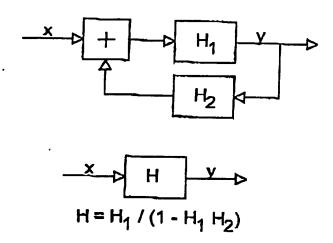

Equivalent low-pass representation

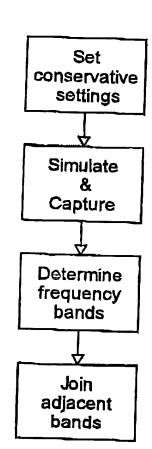

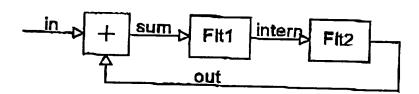

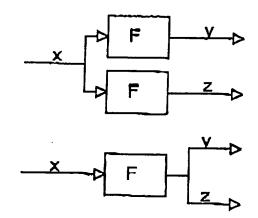

Figure 3

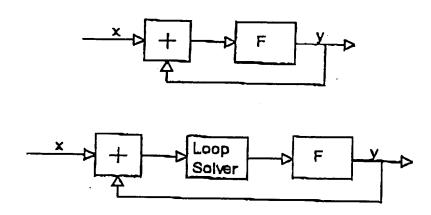

Figure 4

that that one that that the the test of the test of

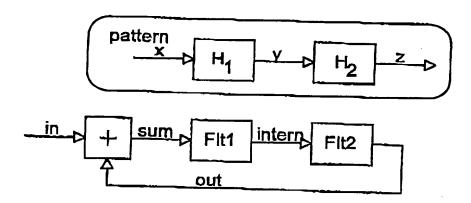

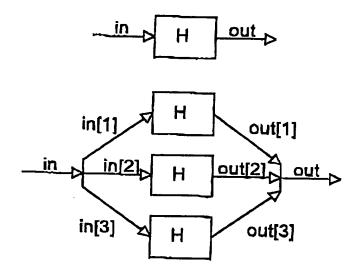

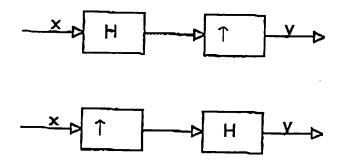

Figure 5

Pigure 6

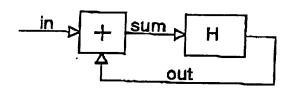

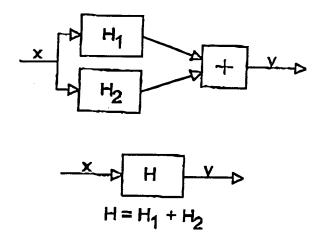

Figure 7

Figure 8

Figure 9

Figure 10

Figure 11

Figure 12

Figure 13

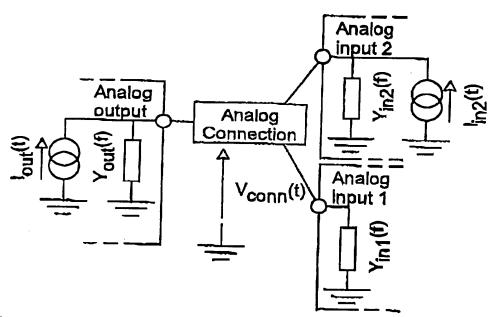

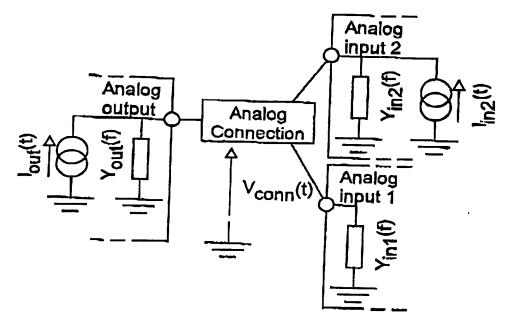

$$|_{\text{in2}} \rightarrow |_{\text{conn}} \rightarrow |_{\text{lin2}} \rightarrow |_{\text{in1}} |_{\text{fin2}} |_{\text{in2}}$$

$$|_{\text{in2}} \rightarrow |_{\text{H(f)}} = (Y_{\text{out}}(f) + Y_{\text{in1}}(f) + Y_{\text{in2}}(f))^{-1}$$

Figure 14

Figure 15

Figure 16

Figure 17

Figure 18

Figure 19

Figure 20

Figure 21

Figure 22

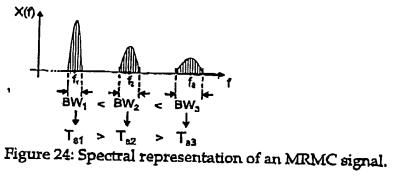

Figure 23

Figure 25

| Input Circuit (graphical, text format) | Perform Preliminary Simulation | Perform Preliminary Simulation  Determine signal representations | Simplify signal representations | Construct Computational graph | Split linear subcircuits   Determine computation   in plurality of nodes   method for nonlinear circuits |  |

|----------------------------------------|--------------------------------|------------------------------------------------------------------|---------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------|--|

| du]                                    | Pe                             | Det                                                              | Sin                             | Con                           | Add up/down sampling nodes                                                                               |  |

Scheduling of computation nodes - preferring vector processing modes

Executed Scheduled Computation Rules

\*! .!

and the second